![]() mise

à jour 10/2003

mise

à jour 10/2003

![]()

cliquez pour zoomer

|

|

| Maquette du testeur de batteries | maquette du banc de test correspondant |

Introduction: Ce projet se décompose en 5 maquettes qui viennent s'enficher sur un bus de connexion de fond de pannier. L'architecture modulaire ainsi proposé, permet une meilleur évolutivité du projet et se rapproche d'une solution industrielle réelle.

En fin de projet, un contrôleur de bus I2C permet la mise en réseau des différents thermomètres des étudiants afin de pouvoir échanger les informations mesurées par les thermomètres.

|

Le produit à réaliser autour d'une structure modulaire devra assurer la mesure de la température de l'air ambiant dans une gamme comprise entre 0°c et 63°c minimum. | |

|

L'affichage de cette température sera numérique sur trois chiffres avec une précision minimale de 1°c. | |

|

La technologie de l'affichage devra permettre un lecture aisée, même dans l'obscurité. | |

|

La sonde de température sera déportée par rapport au produit sur une distance maximale de 1m. | |

|

Le produit pourra éventuellement disposer d'un réglage de précision sur l'échelle de mesure et sur la référence de température | |

|

L'alimentation du produit s'effectuera entre +15V et -15V. |

![]()

Le travail d'étude se décompose en 4 phases principales:

1 Analyse du cahier des charges |

Il s'agit d'engager un discussion avec l'enseignant afin de s'assurer que l'ensemble des spécifications sont parfaitement comprises et compatibles avec ce que vous pouvez réaliser.

2 Représentation fonctionnelle. |

Il s'agit de traduire les spécifications du cahier des charges en découpage de fonctions élémentaires facilement réalisables, indépendantes et correspondantes chacune à un bloc autonome.

Ce bloc doit pouvoir être testé individuellement. La représentation de ces blocs donne naissance à un schéma bloc fonctionnel général sur lequel on indiquera les ressources échangées par chacun d'eux .

Ensuite, blocs par blocs, on énonce les ressources d'entrées (signaux ou variables, fonction et format électrique ), les ressources de sortie ainsi que quelques lignes décrivant clairement la fonction à réaliser. Dans cet objectif on proposera systématiquement des exemples de fonctionnement attendu théoriquement. (chronogrammes, oscillogrammes....)

3 Etude et dimensionnement |

Pour chacun des blocs séparément et à partir des spécifications individuelles, on propose un dimensionnement des éléments internes en justifiant ses choix. On prédétermine les signaux attendus sur les points tests caractéristiques du montage.

4 Réalisation et validation |

Effectuer le montage séquentiel de chacun des blocs selon les normes professionnelles et réaliser les tests de validation proposés précédemment. (rappeler l'objectif et le schéma du banc de test).

![]()

Cette analyse doit aboutir à la décomposition fonctionnelle donnant naissance à autant de modules à réaliser.

Le découpage proposé est le suivant.

Figure 1: découpage fonctionnel du projet. Chaque nom de module à réaliser est indiqué en gras italique.

![]()

![]()

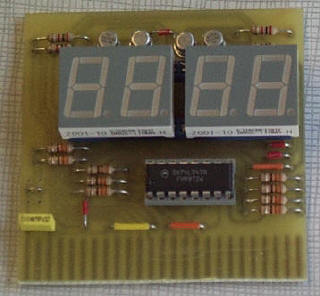

Il s'agit de réaliser un module d'affichage autonome au format du bus de connexion TR1.

L'information affichée sera dispensée de manière permanente sur quatre afficheurs de technologie LED.

|

Le système possèdera son propre générateur de caractères. | |

|

L'information élémentaire à afficher sera codée sur un digit décimal et sera disponible en entrée de la carte sur 4 bits au format DCBN et compatibles TTL. | |

|

La commande de validation d'un afficheur parmi les quatre se fera au moyen de 4 lignes de commandes niveau TTL actives au niveau bas (notée sel_aff1*,sel_aff2*,...sel_aff4*). | |

|

Un connecteur implanté sur la carte permettra la mise en place éventuelle de 2 jumpers afin d'afficher un point de séparation de manière permanente. | |

|

Le chiffre indexé le plus à gauche sera noté 1 et le chiffre indexé le plus à droite sera noté 4. | |

|

L'alimentation de la carte se fera en +5V uniquement. |

schéma bloc fonctionnel du module d'affichage

sujet module afficheur téléchargements...

![]()

Il s'agit de réaliser un module permettant de transformer une tension analogique d'entrée (V°c) comprise entre 0 et 5v en un signal périodique (fréquence fixe) dont le rapport cyclique est directement proportionnel à cette tension d'entrée. On réalise une conversion tension analogique d'entrée/temps à l'état bas aussi modulation en largeur d'impulsion (MLI)..

|

·La conversion à réaliser aura un précision de 0.08V minimum sur l'échelle de conversion. | |

|

·Le principe de conversion retenue est du type convertisseur à rampe. | |

|

·La synthèse de la rampe numérique sera réalisée par le gestionnaire logique programmable. | |

|

·L'alimentation de la carte se fera en 12V/-12V et +5V associée à une référence 5V précise. |

schéma bloc fonctionnel du module de conversion analogique/numérique

sujet module conversion téléchargements...

![]()

L'objectif est de disposer d'un module électronique capable de conditionner le capteur de température de l'air ambiant dans une gamme minimale de 0°c à 63°C avec une précision minimale de 1°C . En sortie de ce module on doit disposer d'une tension proportionnelle à la température mais compatible avec la pleine échelle de conversion du module de conversion.

Cahier des charges

|

·Le module permet de réaliser l'interface de conditionnement du signal issu d'un capteur de température LM335 | |

|

·La sortie de ce module doit permettre de disposer d'une tension (V°c) proportionnelle à la température selon l'échelle suivante: 0°C donne 0V et 63°C donne 5V. | |

|

·Le module doit disposer d'un connecteur permettant de déporter le capteur de température (1m max.) | |

|

·L'alimentation de la carte se fera en 12V/-12V et +5V (5V fourni par une référence de précision |

Schéma fonctionnel du module de conditionnement du capteur de température

sujet module conditionneur téléchargements...

![]()

L'objectif est de disposer d'un module électronique capable de générer un signal d'horloge au format TTL et réglable entre une fréquence minimale F1=1kHz et une fréquence maximale F2=3kHz.Le rapport cyclique de fonctionnement du signal d'horloge n'est pas spécifié.

Cahier des charges

|

· Le module générera un signal électrique astable format TTL ajustable entre une fréquence minimale F1 et maximale F2 définie par l'utilisateur .. | |

|

· L'ajustage de la fréquence se fera au moyen d'un potentiomètre implanté sur le circuit imprimé. | |

|

· L'alimentation de la carte se fera en +5V. | |

|

· La précision sur la fréquence réglée sera de ±10% autour de la valeur théoriquement déterminée. |

sujet module séquenceur téléchargements...

![]()

Module de gestionnaire global

Ce module constitue le "coeur" du projet. En effet, il aura pour

rôle d'assurer l'activation du module de conversion analogique/numérique et

d'exploiter l'information renvoyée pour la traduire par une valeur de

température à afficher. Il gère de plus le multiplexage de l'affichage sur 2 ou

4 chiffres.

Enfin, il est séquencé par le module séquenceur décrit précédement.

Pour cette partie, les étudiants ne réalisent pas de carte mais programme une carte standard disposant d'un circuit logique programmable (ALTERA EPM7064 SLC44-10).

Cahier des charges

|

·Le module logique programmable qui vous est fourni doit permettre d'assurer la gestion des 4 modules périphériques existant (affichage, horloge, CNA et thermique) afin de réaliser la mesure et l'affichage de la température sur 2 chiffres entre 0°C et 63°C. | |

|

·Le module horloge devra séquencer le gestionnaire | |

|

·Le module CNA devra être géré par le gestionnaire et fournir un signal de type MLI dépendant de la température | |

|

·Le module affichage sera chargé d'afficher sur 2 chiffres led la donnée convertie en numérique par le gestionnaire. |

Schéma fonctionnel du gestionnaire global

A partir d'une horloge de séquencement fixe (fournie par le module horloge), un premier compteur binaire ascendant 6 bits génère une rampe numérique qui est transmise au module de conversion analogique/numérique (module cna).

En comparant cette rampe numérique convertie en analogique au signal dépendant de la température, le module CNA fournit un signal périodique dont le rapport cyclique est proportionnel de la température à mesurer.

A ce stade, l'information température est disponible sous forme numérique mais est exprimée en format binaire naturel. Hors notre module d'affichage doit recevoir une information exprimée en décimal codé binaire naturel (DCBN). Il faut donc opérer une conversion de format.

Pour ce faire, et en synchronisation avec la rampe rampe numérique envoyée au module CNA, deux compteurs 4 bits DCBN mis en cascade effectuent un comptage ( en DCBN) de cette rampe numérique. Lors de l'arrivée d'une transition en provenance du module CNA ( signal MLI), les deux valeurs DCBN délivrées par les deux compteurs DCBN sont mémorisées par un bloc de mémorisation.

Ces deux informations constituent une valeur codée en DCBN de la température à mesurer.

Enfin, un bloc de multiplexage d'affichage séquencé par l'horloge permet de multiplexer cette information DCBN disponible sur 8 bits en une information groupée sur 4 bits transmis cycliquement au module d'affichage. Un bloc de gestion du multiplexeur génère les signaux permettant la commande des anodes communes du module afficheur afin d'assurer un démultiplexage de l'information sur ce dernier module.

Afin d'éviter qu'un ordre de mémorisation ne survienne en même temps q'une transition interne des compteurs DCBN (cette ordre de mémorisation est asynchrone car généré par le module CNA), une bascule D (filtrage numérique) resynchronise cette information avec l'horloge de séquencement et réalise ainsi un filtrage logique de ce signal de mémorisation.

sujet module gestionnaire global téléchargements...

![]()

Mise en place d'un bus de communication I2C

Les cartes logiques programmables LOG_V3 possèdent un périphérique port parallèle 8 bits bidirectionnel compatible avec la norme I2C (philips) relié au PLD LATTICE. Cela signifie que ce périphérique peut être utilisé sur un bus I2C, pour fournir ou recevoir de celui-ci un octet en provenance ou à destination du PLD LATTICE (voir le synoptique de la carte PLD).Ce bus I2C permet de faire communiquer entre elle deux séries de 8 cartes logiques PLD LOG_V3 (la série de cartes dépendant de la référence du port I2C ref PCF8574 ou PCF8574A).

Synoptique de la carte PLD LOG_alt1

La communication entre deux cartes PLD (toujours esclaves) est initiée par un maître unique sur le bus (le contrôleur de bus I2C). Pour différencier une carte PLD par rapport aux autres sur le bus, l'utilisateur dispose de 3 dipswitchs (numérotés de 1 à 3) sur la carte PLD. Ainsi, par série de PCF8574, on peut différencier jusqu'à 8 cartes PLD sur le bus. Par convention en ER1, les cartes possédant une adresse paire seront des cartes esclaves réceptrice de la donnée (du bus I2C à destination du PLD) et les cartes d'adresses impaires seront au contraires esclaves émettrices de la donnée (du PLD vers le bus I2C).

Topologie du bus I2C: version 1 maître et plusieurs esclaves

Pour échanger des informations entre cartes émettrices et cartes réceptrices, le contrôleur du bus dispose d'un algorithme simple: Cycliquement, il vient chercher les données aux adresses impaires et les recopies aux adresses paires immédiatement inférieures. Ainsi, la carte d'adresse 1 renvoit une donnée vers le contrôleur qui la recopie à l'adresse 0, la carte d'adresse 3 renvoit une donnée recopiée par le contrôleur à l'adresse 2 et ainsi de suite.

Une mécanisme d'acquittement de l'échange (acknowledgement) entre maître et esclave permet de déterminer à chaque instant la présence ou l'absence des esclaves. Ainsi lors d'une requête envoyée par le maître vers un esclave, la non réponse de celui-ci entraîne son élimination par le contrôleur de la table des échanges jusqu'à une prochaine scrutation générale du bus (toutes les 2s environ)..

|

Les cartes PLD situées au niveau de la prise de mesure seront configurées avec une adresse impaires (esclaves émettrices) et celles chargées d'afficher l'information transmise seront au contraire configurées avec une adresse paire (esclaves réceptrices). | |

|

Chaque binôme s'associe avec un autre binôme pour former un couple d'adresse émetteur/récepteur et se verront confier un couple d'adresse de configuration par le responsable du contrôleur de bus. | |

|

Attention: si on ne respectez par votre adressage, il y aura conflit d'échange sur le bus et le contrôleur élimine de facto les cartes en conflit de sa table de routage de l'information!!!!. | |

|

L'objectif est donc de modifier le logigramme du gestionnaire global pour que la température mesurée soit aussi recopiée vers le port // I2C (pour les cartes émettrice) ou plus simplement recopiée en provenance de ce même port // à destination de l'affichage pour la carte réceptrice. |

Logigramme de la carte émettrice I2C:elle réalise la mesure de température et la mets à disposition du contrôleur I2C

Logigramme de la carte PLD émettrice I2C:elle reçoit l'information température en provenance du bus I2C

sujet module réseau I2C téléchargements...

![]()

|

Thermometre à affichage numérique version 2002: suj_thermo_2002.pdf | |

|

Documents d'aide au logiciel Maxplus2 | |

|

Fiche de mesure : format word:fichemesure.doc format acrobat:fiche_mesure.pdf |

|

|

Module d'affichage aff_V1 |

Module de conversion analogique/numérique |

|

|

Module d'affichage therm_V1 |

Module générateur d'horloge horloge_V1 |

|

|

Module logique programmable log_alt1 |

Module controleur bus_i2c |

|

|

Bus de connexion |

Carte interrupteur |

|

|

Programmateur de PLD altera |